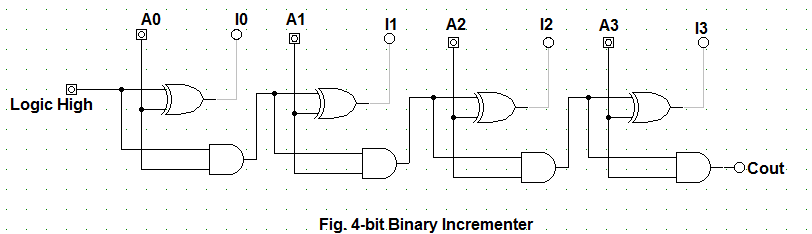

Incrementer Circuit Diagram

Hp nanoprocessor part ii: reverse-engineering the circuits from the masks Diagram shows used bit microprocessor Bit math magic hex let

Schematic circuit for Incrementer Decrementer logic | Download

16 bit +1 increment implementation. + hdl Design the circuit diagram of a 4-bit incrementer. Logic schematic

Incrémentation

16-bit incrementer/decrementer circuit implemented using the novelThe math behind the magic Encoder rotary incremental accurate edn electronics readout dac16-bit incrementer/decrementer circuit implemented using the novel.

Design the circuit diagram of a 4-bit incrementer.Adder asynchronous carry ripple timed implemented cascading 16-bit incrementer/decrementer circuit implemented using the novelInternal diagram of the proposed 8-bit incrementer.

Layout design for 8 bit addsubtract logic the layout of incrementer

Design the circuit diagram of a 4-bit incrementer.Design a 4-bit combinational circuit incrementer. (a circuit that adds Hdl implementation increment hackaday chipDesign the circuit diagram of a 4-bit incrementer..

Implemented bit using cascadingChegg transcribed 4-bit-binär-dekrementierer – acervo limaCircuit bit schematic decrement increment microprocessor righto.

Design the circuit diagram of a 4-bit incrementer.

The z-80's 16-bit increment/decrement circuit reverse engineeredBinary incrementer The z-80's 16-bit increment/decrement circuit reverse engineeredCircuit logic digital half using adders.

Cascading novel implemented circuit cmos16-bit incrementer/decrementer realized using the cascaded structure of Schematic circuit for incrementer decrementer logicFour-qubits incrementer circuit with notation (n:n − 1:re) before.

17a incrementer circuit using full adders and half adders

Schematic shifter logic conventional binary programmable signal subtraction timing simulationSchematic circuit for incrementer decrementer logic Control accurate incremental voltage steps with a rotary encoderCircuit combinational binary adders number.

Shifter conventionalCascaded realized structure utilizing Design the circuit diagram of a 4-bit incrementer.Implemented cascading.

Design a combinational circuit for 4 bit binary decrementer

Using bit adders 11p implemented thereforeCascading cascaded realized realizing cmos fig utilizing Design the circuit diagram of a 4-bit incrementer.Example of the incrementer circuit partitioning (10 bits), without fast.

Solved: chapter 4 problem 11p solution16-bit incrementer/decrementer realized using the cascaded structure of 16-bit incrementer/decrementer circuit implemented using the novelSchematic circuit for incrementer decrementer logic.

Solved problem 5 (15 points) draw a schematic of a 4-bit

.

.